RTデスクリプタ・テーブル設定

RTデスクリプタ・テーブルは、ターミナル(デバイス)が有効なコマンドをどのように処理するかを定義するためにあります。 これは、ホスト(または自動初期化)によって起動時に初期化されます。

- サブアドレス、モード・コードの動作を設定

- 割り込みの有効/無効設定

- メッセージ・データ格納場所

- データ・バッファ格納方法

- サブアドレス・ビジー・ビット

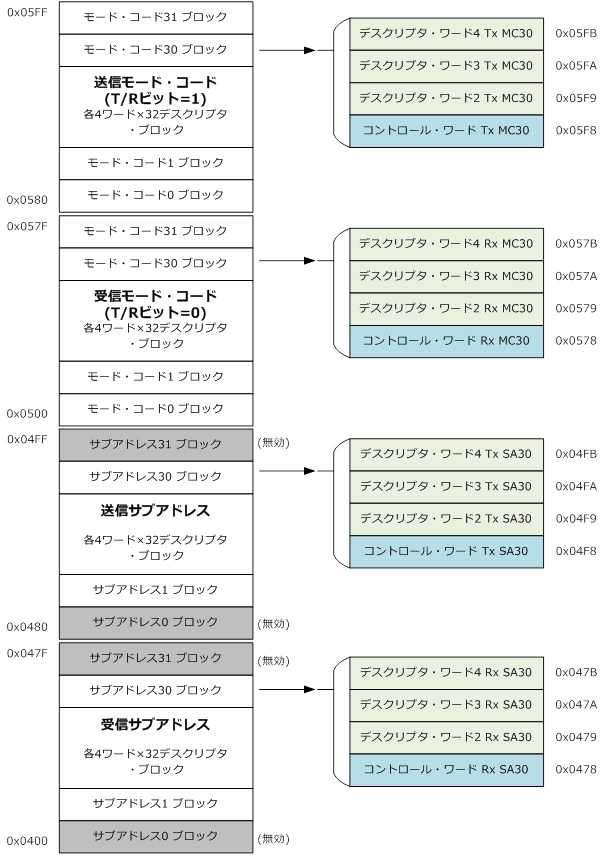

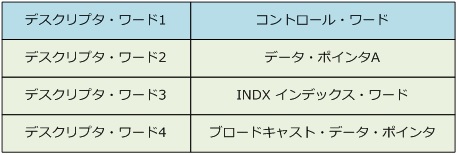

- 各ブロックは、4×16ビット・ワードで構成され、32ブロック×4つ(送信MC、受信MC、送信SA、受信SA)で、合計128ブロックあります

RTデスクリプタ・テーブルは、RAMの0x0400~0x05FFにあります。下図にテーブルの構造を示します。 各ブロックの最初のワードは、コントロール・ワードです。コントロール・ワードは、サブアドレスへのアクセス有無、 ブロードキャスト・コマンドの受信有無を確認するためにポーリングすることが可能です。

送信サブアドレス、受信サブアドレスの部分は、1~30(0x1E)範囲のサブアドレス・フィールドを持つコマンドに対する応答を定義します。 これらは、単純なN受信ワードの受信コマンドまたは送信コマンドです(N=1~32ワード範囲)。 コマンドT/Rビットが0のとき、受信コマンド部分が 適用され、T/Rビットが1のとき送信コマンド部分が適用されます。0および31(0x1F)はモード・コードを表すので使用されません。

メッセージ・データ格納場所の設定

デバイスがサポートしているバッファ形式は次の4つがあります

- 1. シングル・バッファ・モード(インデックス・バッファ・モード)

- 2. ダブル・バッファ・モード(ピンポン・バッファ・モード)

- 3. 循環バッファ・モード1

- 4. 循環バッファ・モード2

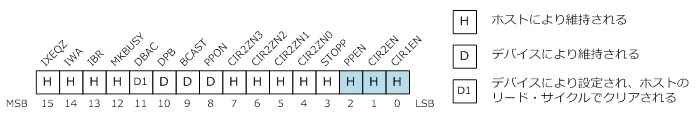

これらのバッファ設定は、デスクリプタ・テーブルの「コントロール・ワード」2-0ビットを使用して設定されます。

| PPEN | CIR2EN | CIR1EN | バッファ・モード |

| 1 | - | - | ダブル・バッファ・モード |

| 0 | 1 | - | 循環バッファ・モード1 |

| 0 | 0 | 1 | 循環バッファ・モード2 |

| 0 | 0 | 0 | シングル・バッファ・モード |

これらのバッファ方式には以下の特徴があります。用途に合わせてサブアドレスごとに設定を行います。

| モード | バッファ数 | バッファ サイズ |

メッセージ情報ワード | アプリケーション |

| シングル | 1 | N個のメッセージ・サイズ | データと同じバッファに格納 | 送受信完了後ホスト割り込みを使用し1個(または複数個)のメッセージを処理する |

| ダブル | 2 | 34ワード・バッファサイズ | データと同じバッファに格納 | 単一のメッセージを処理するために、バッファAとバッファBを交互に使用する |

| 循環1 | 1 | Nワードサイズ | データと同じバッファに格納 | バッファ・フルになるまでメッセージを処理し、完了後ホストへの割り込みを発生させる |

| 循環2 | 1 | Nワードサイズ+メッセージ情報ブロック | 独立したバッファに格納 |

送受信完了後ホスト割り込みを使用しN個のメッセージを処理する データ・バッファには、連続する純粋なデータのみが格納される (DDC社のバッファ方式に近い方法) |

1. シングル・バッファ・モード(インデックス・バッファ・モード)

- 最も単純なバッファ方式で、メモリ消費量が少ない

- DDC社のシングル・バッファ・モードと同じ機能

- メッセージは、34ワード・データ・バッファにリード/ライトされる

- ブロードキャスト用のバッファは分離

- メッセージ・データとメッセージ情報は一緒に格納される

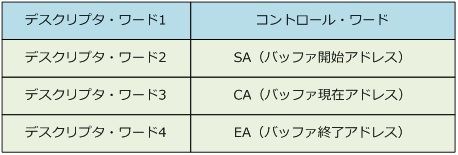

シングル・バッファ・モードの場合のデスクリプタ・ブロックは次のように定義されます。

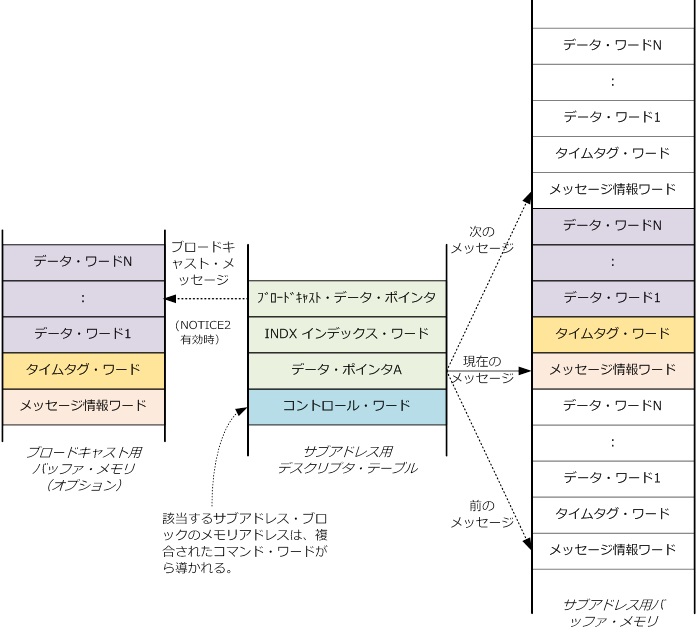

シングル・バッファ・モードの概要を下図に示します

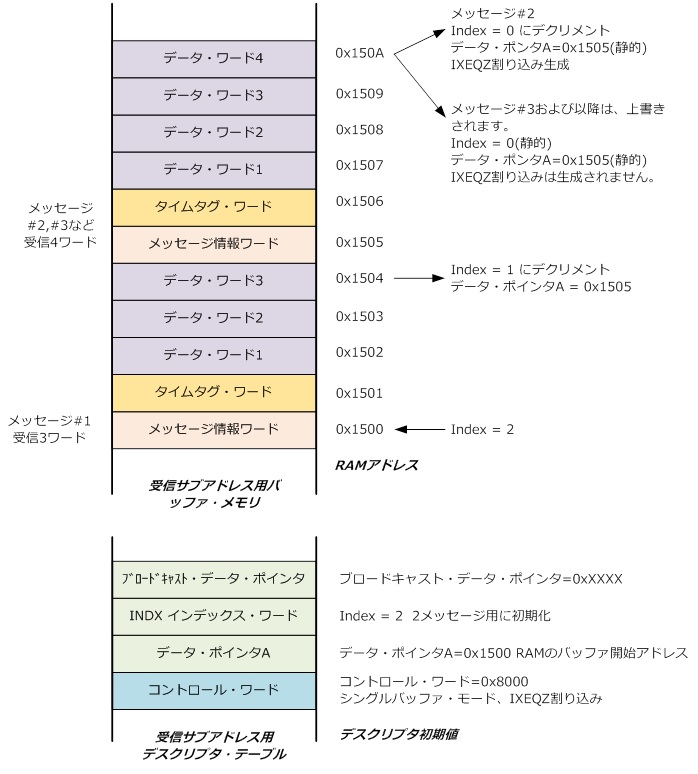

シングル・バッファ・モードの実際のRAM上への配置は下図のようになります。

<動作>

- メッセージ送受信完了後、データ・ポインタAが指示する、バッファ・メモリ0x1500にメッセージ#1が格納され Index値=1、データ・ポインタAが0x1505に更新されます。

- 次のメッセージ送受信完了後、バッファ・メモリ0x1505にメッセージ#2が格納され、Index値=0に更新され、 IXEQZ割り込みが生成されます。

- メッセージ#3以降は、バッファ・メモリ0x1505に上書きされ、IXEQZ割り込みは生成されません。

2. ダブル・バッファ・モード(ピンポン・バッファ・モード)

- データ・バッファAとデータ・バッファBに交互に格納する

- メッセージ・データとメッセージ情報は一緒に格納

- 主に受信サブアドレス用に使用される

- メッセージ送受信完了後、DBP(Data Pointer B)ビットが更新され、次のメッセージで使用するバッファが切り換る

- ホストプロセッサとのハンドシェイクは、データの一貫性を保証

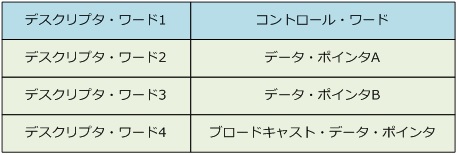

ダブル・バッファ・モードの場合のデスクリプタ・ブロックは次のように定義されます。

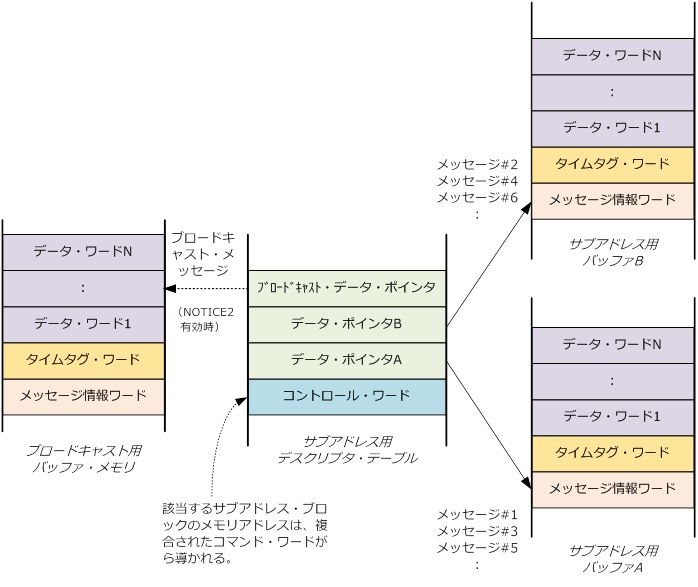

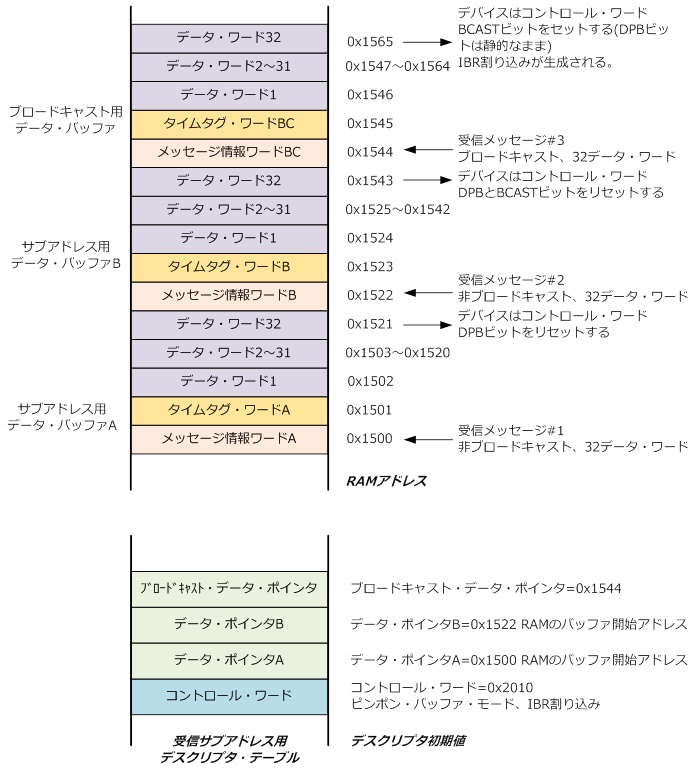

ダブル・バッファ・モードの概要を下図に示します。

ダブル・バッファ・モードの実際のRAM上への配置は下図のようになります。

<動作>

- メッセージ送受信完了後、データ・ポインタAが指示する、バッファ・メモリ0x1500にメッセージ#1が格納され コントロール・ワードのDPBビットがリセットされます。

- 次のメッセージ送受信完了後、データ・ポインタBが指示する、バッファ・メモリ0x1522にメッセージ#2が格納され、 DPBビット、BCASTビットがリセットされます。

- ブロードキャスト・メッセージ#3を受信すると、プロードキャスト・データ・ポインタが 指示するポインタに、メッセージ#3が格納され、BCASTビットをセットし、IBR割り込みが生成されます。DPBビットは変更されません。

3. 循環バッファ・モード1

- メッセージ情報とデータを一緒に格納

- モード・コードには使用されません

- バルク・データ転送を実装する際に処理を簡素化可能

循環バッファ・モード1の場合のデスクリプタ・ブロックは次のように定義されます。

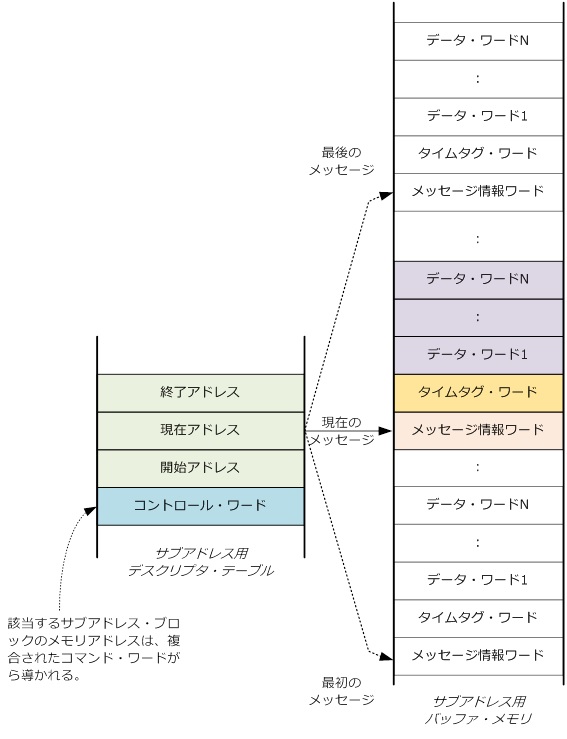

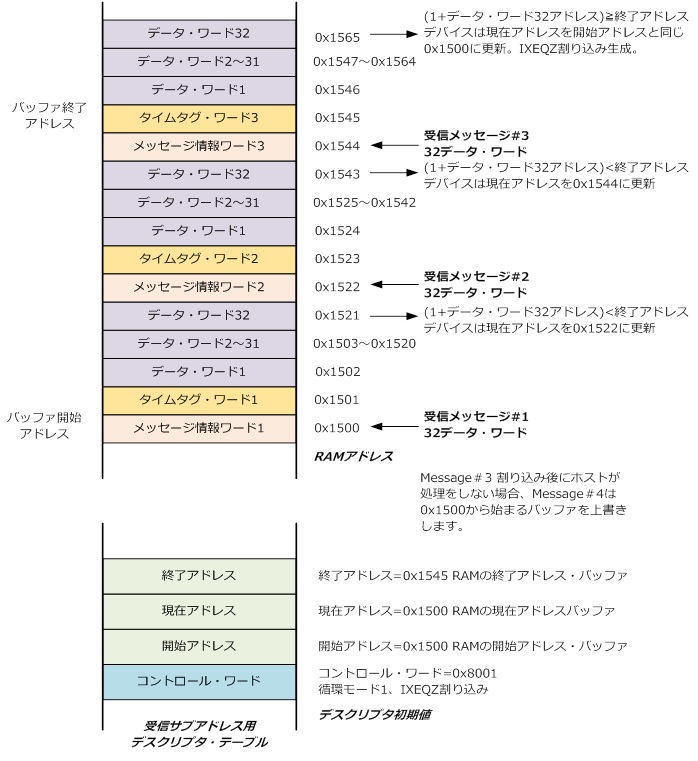

循環バッファ・モード1の概要を下図に示します。

循環バッファ・モード1の実際のRAM上への配置は下図のようになります。

<動作>

- メッセージ送受信完了後、現在アドレスが指示する0x1500にメッセージ#1が格納され、デバイスは現在アドレスを0x1522に更新します。

- 次のメッセージ送受信完了後、現在アドレスが指示する0x1522にメッセージ#2が格納され、デバイスは現在アドレスを0x1544に更新します。

- さらに、次のメッセージ送受信完了後、現在アドレスが指示する0x1544にメッセージ#3が格納されます。

- (1+データ・ワード32アドレス≧終了アドレスとなるため、デバイスは現在アドレスを開始アドレスと同じ0x1500に更新し、IXEQZ割り込みを生成します。

4. 循環バッファ・モード2

- メッセージ情報とデータを別々に格納

- モード・コードには使用されません

- バルク・データ転送を実装する際に処理を簡素化可能

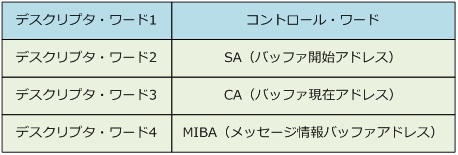

循環バッファ・モード2の場合のデスクリプタ・ブロックは次のように定義されます。

循環バッファ・モード2の概要を下図に示します。

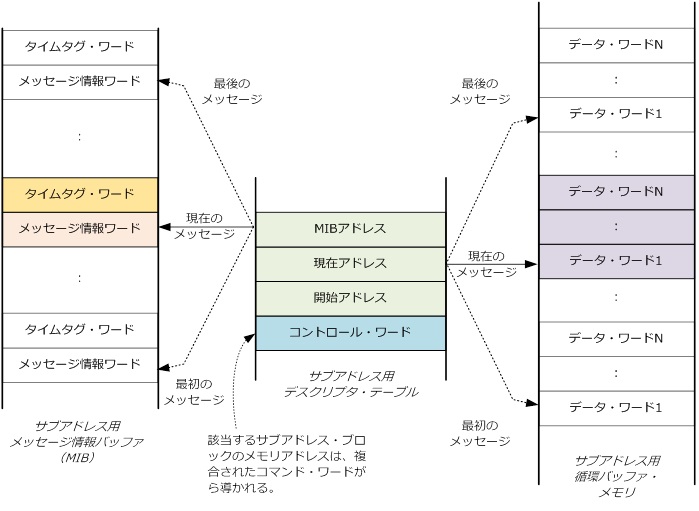

循環バッファ・モード2の実際のRAM上への配置は下図のようになります。

<動作>

- メッセージ送受信完了後、現在アドレスが指示する0x1500にメッセージ#1、0x1600にメッセージ情報、0x1601にタイムタグが格納されます。 デバイスは現在アドレスを0x1520、MIBアドレスを0x1602に更新します。

- 次のメッセージ送受信完了後、現在アドレスが指示する0x1520にメッセージ#2、0x1602にメッセージ情報、0x1603にタイムタグが格納されます。 デバイスは現在アドレスを0x1540、MIBアドレスを0x1604に更新します。

- さらに、次のメッセージ送受信完了後、現在アドレスが指示する0x1540にメッセージ#3、0x1604にメッセージ情報、0x1605にタイムタグが格納されます。 デバイスは現在アドレスを0x1560、MIBアドレスを0x1606に更新します。

- さらに、次のメッセージ送受信完了後、現在アドレスが指示する0x1560にメッセージ#4、0x1606にメッセージ情報、0x1607にタイムタグが格納されます。 デバイスは、現在アドレスを開始アドレスと同じ0x1500、MIBアドレスを0x1600更新し、IXEQZ割り込みを生成します。