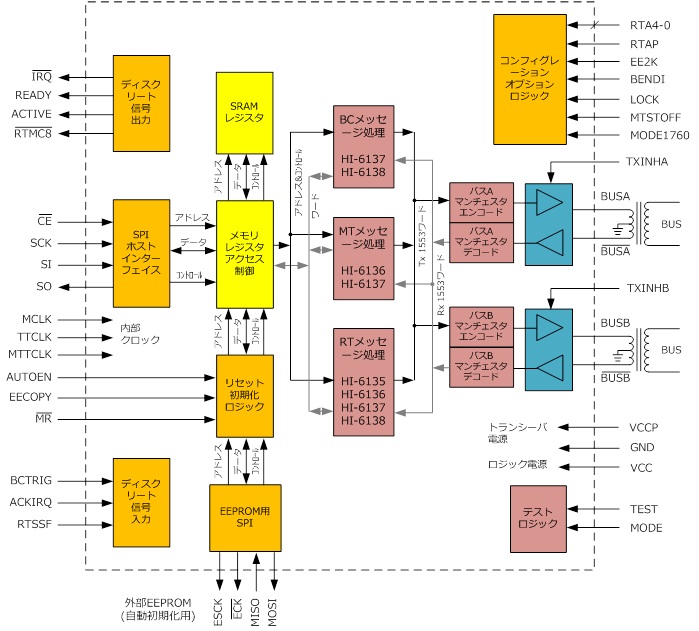

ブロック図

下記に、HI-6138/37/36/35 のブロック図を示します。

| ピン | 機能 | 説明 |

| CLK | 入力 50kΩ プルダウン |

マスター・クロック入力、50.0MHz±100ppm |

| TTCLK MTTCLK |

入力 50kΩ プルダウン |

オプション・クロック入力BC基準タイムおよび、RTタイムタグ・カウンタ オプション・クロック入力タイムタグ・カウンタ 各機能の(BC、MT、RT)には独立したタイムタグ・カウンタがあります。 BCおよび、RTカウンタは共通クロックを共有しますが、内部生成周波数または外部クロック入力から選択できます。 MTタイムタグ・カウンタは、それ自身の外部または内部クロック・ソースを持ちます。 |

| MR | 入力 50kΩ プルアップ |

マスター・リセット、アクティブLow ホストは、「Master Status and Reset Register (0x0001)」のビットを セットすることによってソフトウェア・リセットをアサートすることもできます。 |

| TXINHA TXINHB |

入力 50kΩ プルアップ |

バスAおよびBの送信禁止、アクティブHigh これらの2つの入力は、バスAまたはバスBの送信を有効または無効にするために、 「Master Configuration Register 1 (0x0000)」の対応するビットのペアと論理和を取ります。 |

| MTSTOFF | 入力 50kΩ プルダウン |

メモリ・テスト無効、アクティブHigh このピンがLowのとき、デバイスは、MRリセット・ピンの立ち上がりエッジの後にRAM全体の メモリ・テストを実行します。このピンがHighのとき、RAMテストはスキップされリセット処理が高速になります。 詳細は「リセットと初期化」を参照してください。 |

| AUTOEN | 入力 50kΩ プルダウン |

自動初期化有効、アクティブHigh このピンがMRリセット・ピンの立ち上がりエッジでHighレベルの場合、 自己初期化が進行し、コンフィグレーション・データが専用のEEPROM SPIポートを介して 外部シリアルEEPROMからレジスタおよびRAMにコピーされます。 |

| EE2K | 入力 50kΩ プルダウン |

AUTOENピンがHighのとき、EE2K入力は自動初期化処理の範囲を設定します。 EE2KがLowのとき、0x0~0x1FFFまでの8Kアドレス範囲を占有するレジスタとRAMが初期化されます。 高速初期化を必要とするアプリケーションでは、EE2KがHighのとき、0x0~0x07FFまでの2Kアドレス範囲を占有するレジスタとRAMのみが初期化されます。 AUTOENピンがLowの場合、このピンは使用されません。 |

| READY | 出力 | 自動初期化またはビルドイン・テスト中の場合、このピンはLowです。 ピンの状態がLowのとき、ホストはデバイスRAMまたはレジスタをリード/ライトできません。 いずれかのアドレスをリードすると「Master Status and Reset Register (0x0001)」の値が返されます。 マスター・リセット時にAUTOENピンがLowレベルのとき、ホストはREADYがHighレベルになった後、 デバイスRAMとレジスタをコンフィグレーションすることができます。 |

| ACTIVE | 出力 | デバイスが1553メッセージを処理している間はHighです。 |

|

ECS ESCK MOSI MISO |

出力 出力 出力 入力 50kΩ プルダウン |

マスター・リセット時にAUTOENがHighのとき自動自己初期化に使用されるオプションの 外部EEPROMに接続するための専用4線式SPIインターフェイス。 |

| EECOPY | 入力 50kΩ プルダウン |

EEPROMコピー、アクティブHigh この入力をアサートすると、 自動初期化に使用されるEEPROMにRAMおよびレジスタのコピーが開始されます。 |

| MODE1760 | 入力 50kΩ プルダウン |

Mode1760有効、アクティブHigh ハードウェアリセット中にこのピンをアサートして1760モードを有効にします。 1760モードでは、デバイスはステータス・ワードにBusyがセットされた有効なコマンド(RTアドレスが一致する)に 応答します。データ・ワードは送信されず、割り込みやデータロギングも発生しません。 |

| LOCK | 入力 50kΩ プルダウン |

MRピンに立ち上がりエッジが発生すると、ピン状態はRT動作ステータス・レジスタのロックビットにラッチされます。 ステータス・レジスタのロックビットがHighの場合、ホストは同じレジスタ内のターミナル・アドレスを上書きできません。 ステータス・レジスタのロックピットがローの場合、ホストはRT動作ステータス・レジスタのターミナル・アドレスとパリティ(および、ロックビット)を 上書きすることができます。 |

| RTMC8 | 出力 オープンドレイン |

RT「リセットRT」モード・コマンド(MC8)受信 このアクティブLow出力は、RTが「リセットRT」モード・コマンドを受信したときに、ステータス・ワードの完了時にアサートされます。 最小出力パルス幅は100nsで、MRアサートの影響を受けません。 |

| RTSSF | 入力 50kΩ プルダウン |

RTサブシステム・フェイル入力、アクティブHigh このアクティブLow出力は、RTが「リセットRT」モード・コマンドを受信したときに、ステータス・ワードの完了時にアサートされます。 最小出力パルス幅は100nsで、MRアサートの影響を受けません。 |

| IRQ | 出力 オープンドレイン |

割り込みリクエスト、アクティブLow このピンは有効にされた割り込みイベントが発生するたびにアサートされます。 「Master Configuration Register 1 (0x0000)」のINTSELビットによって、 短時間のLowパルス出力またはレベル出力としてプログラミングされています。 レベル出力が選択されている場合、ホストはACKIRQピンの立ち上がりエッジをパルスすることによって ホストがIRQを認識するまでLowです。 |

| ACKIRQ | 入力 50kΩ プルダウン |

割り込みACK、アクティブHigh この入力は、RTコンフィグレーション・レジスタのINTSELビットがHighのときに使用され、 IRQピンのレベル割り込みアサートを有効にします。割り込みアサートによってIRQピンがLowになると、 ACKIRQ(250nsecの最小時間)のHighパルスがIRQ出力を論理1にクリアします。 |

| RTA4:0 RTAP |

入力 50kΩ プルアップ |

RTアドレス・ビット4-0およびパリティ・ビット RTAPピンは、RTA4:0ピンのアドレスに奇数パリティを提供します。 MRピンに立ち上がりエッジが発生すると、ターミナル・アドレス・レベルとパリティ・ピン・レベルが RT動作ステータス・レジスタにラッチされます。RT動作ステータス・レジスタの値(これらのピンではない)は、 アクティブなターミナル・アドレスを反映します。 |

| BENDI | 入力 50kΩ プルダウン |

ビッグ・エンディアンのコンフィグレーション・ピンで、バイト転送を使用するときに

「エンディアン」またはバイト順序を選択します。 エンディアンは、整数が最下位バイト(ビッグ・エンディアン)または 最上位アドレス(リトルエンディアン)に格納されているかどうかを示すシステム属性です。 内部レジスタ/RAMの格納は「ビッグ・エンディアン」です。 このピンは、SPIコマンドに続いて転送される16Bitデータのバイト順を制御します。 BENDIがLowのときは、「リトルエンディアン」が選択されます。 下位バイト(Bit 7:0)は上位バイト(Bit 15:8)の前にSPIで処理されます。 BENDIがHighのとき、ビッグ・エンディアンが選択され、下位バイトの前にSPIで上位バイトが処理されます。 |

| TEST | 入力 50kΩ プルダウン |

テスト有効入力 ホストはこのピンをアサートして、 RAMセルフ・テストおよびループバック・テストを実行します。 |

| BCTRIG | 入力 50kΩ プルダウン |

BCトリガ入力、アクティブHigh 特定のBC命令と併せて使用します。 |

| MODE | 入力 50kΩ プルアップ |

工場テスト用に使用されるピン 接続しないでください。 |

| VCC VCCP GND |

電源供給 | ロジックおよびバス・トランシーバ用の3.3VDC電源 |

| BUSA BUSA |

アナログ |

外部MIL-STD-1553絶縁トランスへの双方向バスAインターフェイス 正/負の極性を注意してください |

| BUSB BUSB |

アナログ |

外部MIL-STD-1553絶縁トランスへの双方向バスBインターフェイス 正/負の極性を注意してください |